Document No.: IAP-ELI501-00

# APPROVAL SHEET

| Product              | Battery Protect Solution IC        |

|----------------------|------------------------------------|

| Product code         | <b>ELI501</b><br>( 001-ELI501-00 ) |

| Production Form      | TEP - 5L,BD54                      |

| Date of Registration | July. 16. 2009                     |

|        | Issued | Checked  | Checked | Approved |

|--------|--------|----------|---------|----------|

| 결<br>재 | A      | Spa      | 2/      | John     |

|        | H.M Jo | S.W Park | S.H Ahn | Y.S Kim  |

|    | 番 望   | 7 全  |  |

|----|-------|------|--|

| 협  | 9/20  |      |  |

| 의  | 0/83  | 原源   |  |

| -1 | ial a | n/-  |  |

|    | n/2   | 11/2 |  |

Room 2504 International Science & Technology Building, Shen Nan Middle Road,Futian,Shen Zhen

TEL:+86-0755-83957788 / +86-0755-82566617

FAX:+86-0755-23919567 E-mail:li@itm-cn.com

## **■** Contents

| 1.  | Features                                                                | Page | 1  |

|-----|-------------------------------------------------------------------------|------|----|

| 2.  | Outline                                                                 | Page | 2  |

| 3.  | Pin Assignment                                                          | Page | 3  |

| 4.  | Block Diagram                                                           | Page | 3  |

| 5.  | Absolute Maximum Rating                                                 | Page | 4  |

| 6.  | Electrical Characteristics                                              | Page | 4  |

| 7.  | Measuring Circuit                                                       | Page | 7  |

| 8.  | Operation ————————————————————————————————————                          | Page | 8  |

|     | 1) Overcharge detector (VD1)                                            | Page | 8  |

|     | 2) Overdischarge detector (VD2)                                         | Page | 8  |

|     | 3) Discharge overcurrent detector, Short detector (VD3, Short Detector) | Page | 9  |

| 9.  | Application Circuit                                                     | Page | 10 |

| 10. | . Timing Chart                                                          | Page | 11 |

| 11. | Packing Spec                                                            | Page | 13 |

|     | . Package Description                                                   | Page | 15 |

| 13. | . Marking Contents                                                      | Page | 16 |

#### **■** Features

- 1. The protection IC and The Dual-Nch MOSFET to use common Drain are integrated into One-packaging IC.

- 2. Reduced Pin-Count by fully connecting internally.

- 3. Application Part

- 1) Protection IC

- ① Uses high withstand voltage CMOS process.

- The charger section can be connected up to absolute maximum rating 24V.

- 2 Detection voltage precision

- Overcharge detection voltage

±60<sup>mV</sup> (Ta=25°C)

- Overdischarge detection voltage

±110<sup>mV</sup> (Ta=25°C)

- Discharging overcurrent detection voltage

±35<sup>mV</sup> (Ta=25<sup>°</sup>C)

- 3 Built-in detection delay times

- Overcharge detection delay time

Min 0.001s / Typ 0.08s / Max 0.20s (Ta=25°C)

- Overdischarge detection delay time)

Min 1<sup>ms</sup> / Typ 40<sup>ms</sup> / Max 100<sup>ms</sup> (Ta=25 $^{\circ}$ C)

- Discharging overcurrent detection delay time)

Min 1<sup>ms</sup> / Typ 10<sup>ms</sup> / Max 30<sup>ms</sup> (Ta=25 $^{\circ}$ C)

- Short detection delay time)

Typ 300 \( \mu \) \( \text{Max 800 \( \mu \) \( \text{Ta=25 °C} \)

- 4 With abnormal charger detection function

- 5 0V charge function is allowed

- 6 Auto Wake-up function is not allowed

- 2) FET

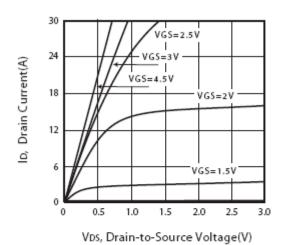

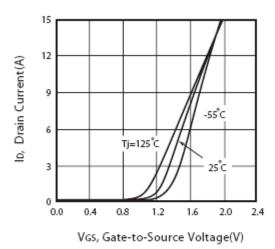

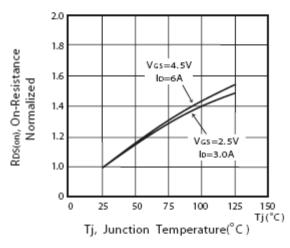

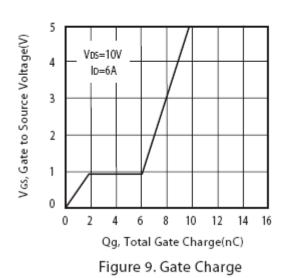

- ① Using advanced trench technology to provide excellent  $R_{DS(ON)}$ , low gate charge and operation with gate voltage as low as 2.5V while retaining a 12V  $V_{GS(MAX)}$ .

- 2 Common drain configuration

- 3 General characteristics

- $V_{DS}$  (V) = 20V

- $I_D (A) = 6A$

- $R_{SS(ON)}$  <  $60m\Omega$  ( $V_{GS}$  = 4.5V,  $I_{D}$  = 1A)

#### Outline

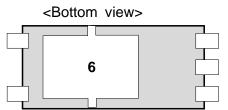

This is a battery protect solution IC which is integrated with built-in the protection IC to use a lithium ion/lithium polymer secondary batteries developed for 1-cell series and Dual-Nch MOSFET. It functions to protect the battery by detecting overcharge, overdischarge, discharge overcurrent and other abnormalities as turning off internal Nch MOSFET.

The protection IC is composed of three voltage detectors, short detection circuit, reference voltage sources, oscillator, counter circuit and logical circuits.

The  $C_{\text{OUT}}$  pin (charge FET control pin) and  $D_{\text{OUT}}$  pin (discharge FET control pin) outputs are CMOS output, and can drive the internal Nch MOSFET directly. The  $C_{\text{OUT}}$  output becomes low level after delay time fixed in the IC if overcharge is detected. The  $D_{\text{OUT}}$  output becomes low level after delay time fixed in the IC if overdischarge, discharge overcurrent or short is detected.

On overcharge state, if the  $V_{\text{DD}}$  voltage is less than the overcharge release voltage, the  $C_{\text{OUT}}$  output becomes high level after delay time fixed in the IC. On overdischarge state, if the voltage of the battery rises more than the overdischarge detection voltage with connecting the charger, the  $D_{\text{OUT}}$  output becomes high level after delay time fixed in the IC. Charging current can be supplied to the battery discharged up to 0V.

Once discharge overcurrent or short have been detected, if the state of discharge overcurrent or short is released by opening the loads, the  $D_{OUT}$  output becomes high level after delay time fixed in the IC. On overdischarge state, the supply current is reduced as less as possible.

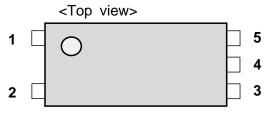

# **■** Pin Assignment

## [ Package: TEP-5L ]

| 1 | TP (N.C)              |

|---|-----------------------|

| 2 | Source 1(same as Vss) |

| 3 | Source 2              |

| 4 | V <sub>DD</sub>       |

| 5 | V-                    |

| 6 | Drain                 |

## **■** Block Diagram

# ■ Absolute Maximum Rating

$\times T_{OPR}=25^{\circ}C$ , Source1(Vss)=0V

| Item                                     | Symbol             | Rating                                      | Unit |

|------------------------------------------|--------------------|---------------------------------------------|------|

| Supply Voltage                           | $V_{DD}$           | -0.3 ~ 10                                   | V    |

| V- Terminal Input Voltage                | V-                 | V <sub>DD</sub> -24 ~ V <sub>DD</sub> +0.3  | V    |

| C <sub>OUT</sub> Terminal Output Voltage | V <sub>соит</sub>  | V <sub>DD</sub> -24 ~ V <sub>DD</sub> +0.3  | V    |

| D <sub>OUT</sub> Terminal Output Voltage | $V_{	extsf{DOUT}}$ | V <sub>SS</sub> -0.3 ~ V <sub>DD</sub> +0.3 | V    |

| Storage Temperature                      | T <sub>STG</sub>   | -40 ~ 125                                   | °C   |

| Drain-Source Voltage                     | V <sub>DS</sub>    | 20                                          | V    |

| Gate-Source Voltage                      | V <sub>GS</sub>    | ±12                                         | V    |

#### **■** Electrical Characteristics

$X T_{OPR}=25$  C

| Item                                      | Symbol              | Measure Condition                           | Min.                 | Тур.                  | Max.  | Unit | *1 |

|-------------------------------------------|---------------------|---------------------------------------------|----------------------|-----------------------|-------|------|----|

| Operating Input Voltage                   | V <sub>DD</sub> 1   | $V_{\text{DD}}$ - $V_{\text{SS}}$           | 1.5                  | -                     | 8.0   | V    | Α  |

| Minimum Operating Voltage for 0V Charging | $V_{\text{ST}}$     | $V_{DD} - V_{-}, V_{DD} - V_{SS} = 0V$      | -                    | -                     | 1.5   | V    | А  |

| C <sub>OUT</sub> Pin Nch ON Voltage       | V <sub>OL</sub> 1   | -                                           | -                    | 0.1                   | 0.5   | V    | -  |

| C <sub>OUT</sub> Pin Pch ON Voltage       | V <sub>OH</sub> 1   | -                                           | V <sub>DD</sub> -0.1 | V <sub>DD</sub> -0.02 | -     | V    | -  |

| D <sub>OUT</sub> Pin Nch ON Voltage       | V <sub>OL</sub> 2   | -                                           | -                    | 0.1                   | 0.5   | V    | -  |

| D <sub>OUT</sub> Pin Pch ON Voltage       | V <sub>OH</sub> 2   | -                                           | V <sub>DD</sub> -0.1 | V <sub>DD</sub> -0.02 | -     | V    | -  |

| Current Consumption                       | I <sub>DD</sub>     | V <sub>DD</sub> =3.9V, V-=0V                | -                    | 3.0                   | 6.0   | μA   | L  |

| Current Consumption at Stand-By           | Is                  | V <sub>DD</sub> =2.0V                       | -                    | -                     | 0.1   | μA   | L  |

| Overcharge Detection Voltage              | V <sub>DET</sub> 1  | R1=100Ω                                     | 4.240                | 4.300                 | 4.360 | V    | В  |

| Overcharge Release Voltage                | V <sub>REL</sub> 1  | R1=100Ω                                     | 4.040                | 4.100                 | 4.160 | V    | В  |

| Overdischarge Detection Voltage           | V <sub>DET</sub> 2  | V-=0V, R1=100Ω                              | 2.290                | 2.400                 | 2.510 | V    | D  |

| Overdischarge Release Voltage1            | V <sub>REL</sub> 2' | V-≥V <sub>CHA</sub> , R1=100Ω               | 2.290                | 2.400                 | 2.510 | V    | D  |

| Overdischarge Release Voltage2            | V <sub>REL</sub> 2' | V-≤V <sub>CHA</sub> , R1=100Ω               | 2.890                | 3.000                 | 3.110 | V    | D  |

| Discharging Overcurrent Detection Voltage | V <sub>DET</sub> 3  | V <sub>DD</sub> =3.6V, R2=1.0 <sup>kΩ</sup> | 0.115                | 0.150                 | 0.185 | V    | F  |

| Short Detection Voltage                   | V <sub>SHORT</sub>  | V <sub>DD</sub> =3.6V                       | 0.55                 | 1.15                  | 1.70  | V    | F  |

| Charger Detection Threshold<br>Voltage    | V <sub>СНА</sub>    | -                                           | -1.2                 | -0.7                  | -0.2  | V    | G  |

Note: \*1 The test circuit symbols.

※ Tope = 25 ℃

| Item                                         | Symbol              | Measure Condition                                                    | Min.  | Тур. | Max. | Unit | *1 |

|----------------------------------------------|---------------------|----------------------------------------------------------------------|-------|------|------|------|----|

| Overcharge Detection<br>Delay Time           | tV <sub>DET</sub> 1 | V <sub>DD</sub> =3.6V→4.5V                                           | 0.001 | 0.08 | 0.20 | S    | В  |

| Overdischarge Detection<br>Delay Time        | tV <sub>DET</sub> 2 | V <sub>DD</sub> =3.6V→2.0V                                           | 1     | 40   | 100  | ms   | D  |

| Discharging Overcurrent Detection Delay Time | tV <sub>DET</sub> 3 | V <sub>DD</sub> =3.6V, V-=0V→1V                                      | 1     | 10   | 30   | ms   | F  |

| Short Detection Delay Time                   | t <sub>short</sub>  | V <sub>DD</sub> =3.6V, V-=0V→3V                                      | -     | 300  | 800  | μs   | F  |

| Drain-Source Breakdown Voltage               | BV <sub>DSS</sub>   | I <sub>D</sub> =250 <sup>\(\mu\A\)</sup> , V <sub>GS</sub> =0V       | 20    | -    | -    | V    |    |

| Zero Gate Voltage Drain Current              | I <sub>DSS</sub>    | V <sub>DS</sub> =16V, V <sub>GS</sub> =0V                            | -     | -    | 1    | μА   |    |

| Gate-Body Leakage Current                    | I <sub>GSS</sub>    | V <sub>DS</sub> =0V, V <sub>GS</sub> =±12V                           | -     | -    | 0.1  | μА   |    |

| Gate-Source Breakdown Voltage                | BV <sub>GSO</sub>   | V <sub>DS</sub> =0V, I <sub>G</sub> =±250 <i>μ</i> A                 | ±12   | -    | -    | V    |    |

| Gate Threshold Voltage                       | $V_{\text{GS(th)}}$ | V <sub>DS</sub> =V <sub>GS</sub> , I <sub>D</sub> =250 <sup>#A</sup> | 0.4   | -    | 0.9  | V    |    |

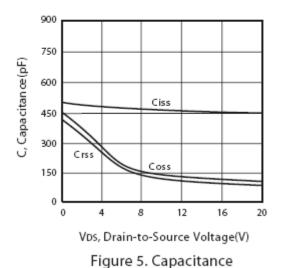

|                                              |                     | V <sub>GS</sub> =10V, I <sub>D</sub> =1A                             | -     | 42   | 50   | mΩ   |    |

| Static Source-Source                         |                     | V <sub>GS</sub> =4.5V, I <sub>D</sub> =1A                            | -     | 50   | 60   | mΩ   |    |

| ON-Resistance                                | R <sub>SS(ON)</sub> | V <sub>GS</sub> =3.9V, I <sub>D</sub> =1A                            | -     | 51   | 61   | mΩ   |    |

|                                              |                     | V <sub>GS</sub> =2.5V, I <sub>D</sub> =1A                            | -     | 62   | 76   | mΩ   |    |

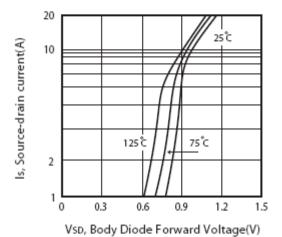

| Diode Forward Voltage                        | $V_{\text{SD}}$     | I <sub>S</sub> =1.7A, V <sub>GS</sub> =0V                            |       | 0.74 | 1.20 | V    |    |

Note: \*1 The test circuit symbols.

\*2 The parameter is guaranteed by design.

Figure 1. Output Characteristics

Figure 3. Body Diode Forward Voltage Variation with Source Current

Figure 2. Transfer Characteristics

Figure 4. On-Resistance Variation with Drain Current and Temperature

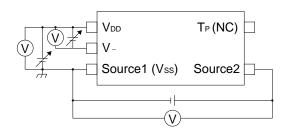

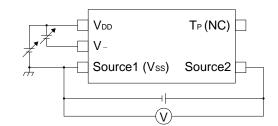

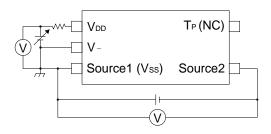

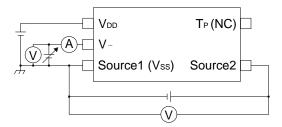

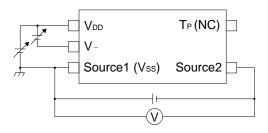

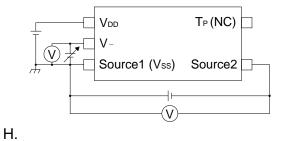

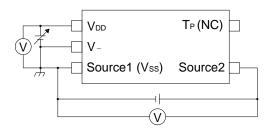

## **■** Measuring Circuit

A.

E.

B.

F.

C.

G.

D.

V<sub>DD</sub> T<sub>P</sub> (NC) V<sub>-</sub> Source1 (Vss) Source2

## Operation

#### 1. Overcharge detector (VD1)

The VD1 monitors  $V_{\text{DD}}$  pin voltage during charge. In the state of charging the battery, it will detect the overcharge state of the battery if the  $V_{\text{DD}}$  terminal voltage becomes higher than the overcharge detection voltage(Typ. 4.300V). And then the  $C_{\text{OUT}}$  terminal turns to low level, so the internal charging control Nch MOSFET turns OFF and it forbids to charge the battery.

After detecting overcharge, it will release the overcharge state if the  $V_{DD}$  terminal voltage becomes lower than the overcharge release voltage(Typ.4.100V). And then the  $C_{OUT}$  terminal turns to high level, so the internal charging control Nch MOSFET turns ON, and it accepts to charge the battery.

When the  $V_{DD}$  terminal voltage is higher than the overcharge detection voltage, to disconnect the charger and connect the load, leave the  $C_{OUT}$  terminal low level, but it accepts to conduct load current via the paracitical body diode of the internal Nch MOSFET. And then if the  $V_{DD}$  terminal voltage becomes lower than the overcharge detection voltage, the  $C_{OUT}$  terminal turns to high level, so the internal Nch MOSFET turn ON, and it accepts to charge the battery.

The overcharge detection and release have delay time decided internally. When the  $V_{\text{DD}}$  terminal voltage becomes higher than the overcharge detection voltage, if the  $V_{\text{DD}}$  terminal voltage becomes lower than the overcharge detection voltage again within the overcharge detection delay time(Typ. 0.08s), it will not detect overcharge. And in the state of overcharge, when the  $V_{\text{DD}}$  terminal voltage becomes lower than the overcharge release voltage, if the  $V_{\text{DD}}$  terminal voltage backs higher than the overcharge release voltage again within the overcharge release delay time, it will not release overcharge.

The output driver stage of the  $C_{\text{OUT}}$  terminal includes a level shifter, so it will output the  $V_{\text{D}}$  terminal voltage as low level. The output type of the  $C_{\text{OUT}}$  terminal is CMOS output between  $V_{\text{DD}}$  and  $V_{\text{D}}$  terminal voltage.

#### 2. Overdischarge detector (VD2)

The VD1 monitors  $V_{DD}$  pin voltage during discharge. In the state of discharging the battery, it will detect the overdischarge state of the battery if the  $V_{DD}$  terminal becomes lower than the overdischarge detection voltage (Typ. 2.400V). And then the  $D_{OUT}$  terminal turns to low level, so the internal discharging control Nch MOSFET turn OFF and it forbids to discharge the battery.

The overdischarge status will be released by two cases:

- (1) When V- pin voltage is equal to or higher than the charger detection voltage ( $V_{CHA}$ ) by charging and the  $V_{DD}$  pin voltage is higher than overdischarge detection voltage (Typ. 2.400V).

- (2) When V- pin voltage is equal to or lower than the charger detection voltage ( $V_{CHA}$ ) by charging and the  $V_{DD}$  pin voltage is higher than overdischarge release voltage (Typ. 3.000V).

When the battery voltage is about 0V, if the charger voltage is higher than the minimum operating voltage for 0V charging (Max. 1.5V), the C<sub>OUT</sub> terminal outputs high level and it accepts to conduct charging current.

The overdischarge detection have delay time decided internally. When the  $V_{DD}$  terminal voltage becomes lower than the overdischarge detection voltage, if the  $V_{DD}$  terminal voltage becomes higher than the overdischarge detection voltage again within the overdischarge detection delay time (Typ. 40ms), it will not detect overdischarge. Moreover, the overdischarge release delay time exists, too.

All the circuits are stopped, and after the overdischarge is detected, it is assumed the state of the standby, and decreases the current (standby current) which IC consumes as much as possible. (When  $V_{DD}=2V$ , Max. 0.1uA).

The output type of the  $D_{\text{OUT}}$  terminal is CMOS output between  $V_{\text{DD}}$  and  $V_{\text{SS}}$  terminal voltage.

#### 3. Discharge overcurrent detector, Short detector (VD3, Short Detector)

In the state of chargable and dischargabe, VD3 monitors the voltage level of V. pin. If the V. terminal voltage becomes higher than the discharging overcurrent detection voltage (Typ. 0.150V) by short of loads, etc., it will detect discharging overcurrent state. If the V. terminal voltage becomes higher then short detection voltage (Typ. 1.15V), it will detect discharging overcurrent state, too. And then the D<sub>OUT</sub> terminal outputs low level, so the internal discharging control Nch MOSFET turns OFF, and it protects from large current discharging.

The discharging overcurrent detection has delay time decided internally. When the V terminal voltage becomes higher than the discharging overcurrent detection voltage, if the V terminal voltage becomes lower than the discharging overcurrent detection voltage within the discharging overcurrent detection delay time (Typ. 10ms), it will not detect discharging overcurrent. Morever, the discharging overcurrent release delay time exists, too.

The short detection delay time (Typ. 300us) decided internally exists, too.

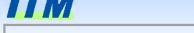

#### ■ Application Circuit (Example)

#### **\*** Application Hint

R1 and C1 stabilize a supply voltage ripple. However, the detection voltage rises by the current of penetration in IC of the voltage detection when R1 is enlarged, so the value of R1 is adjusted to  $100\Omega$  or less. Moreover, adjust the value of C1 to 0.01uF or more to do the stability operation, please.

R1 and R2 resistors are current limit resistance if a charger is connected reversibly or a highvoltage charger that exceeds the absolute maximum rating is connected. R1 and R2 may cause a power consumption will be over rating of power dissipation, therefore the `R1+R2` should be more than 1kohm. Moreover, if R2 is too enlarged, the charger connection release cannot be occasionally done after the overdischarge is detected, so adjust the value of R2 to 5kohm or less, please.

C2 and C3 capacitors have effect that the system stability about voltage ripple or imported noise. After check characteristics, decide that these capacitors should be inserted or not, where should be inserted, and capacitance value, please.

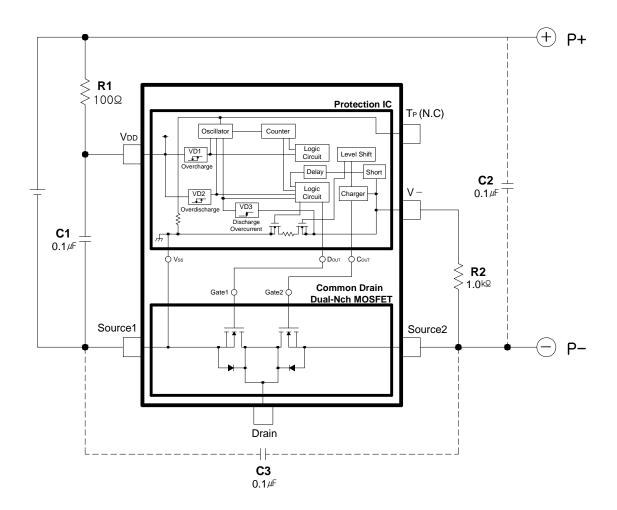

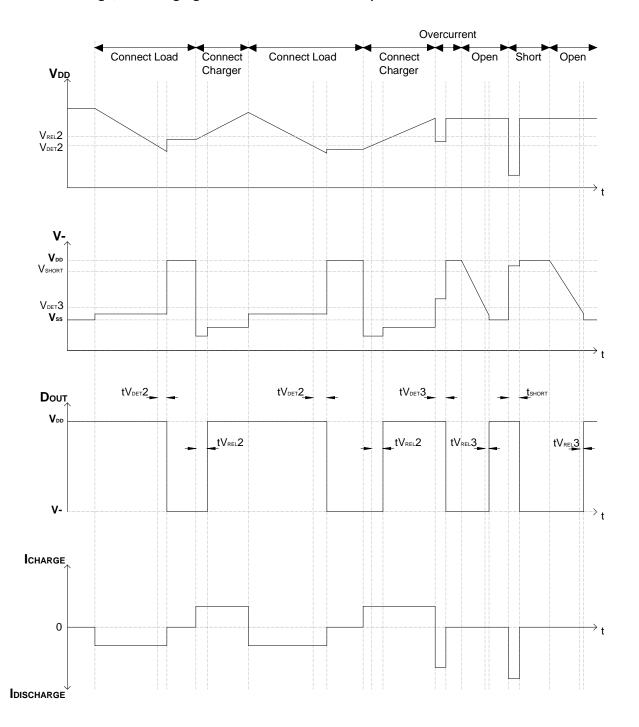

# **■** Timing Chart

## 1. Overcharge operations

## 2. Overdischarge, Discharging Overcurrent and Short operations

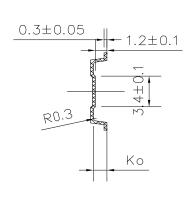

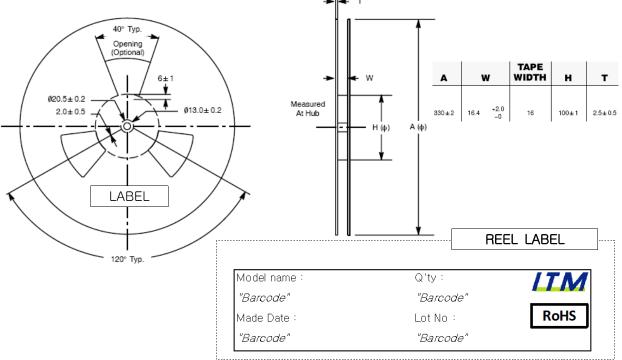

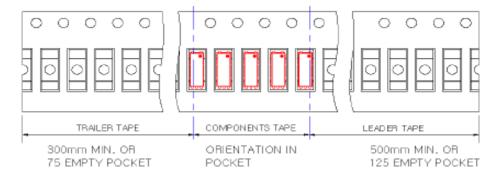

## ■ Packing spec

Ao=2.45±0.1 Bo=6.5±0.1 p1=4±0.1 E=1.75±0.1 F=7.5±0.1 W=16±0.3 Po=4±0.1 Do=Ø1.5-0 Ko=1.4±0.1

##

##

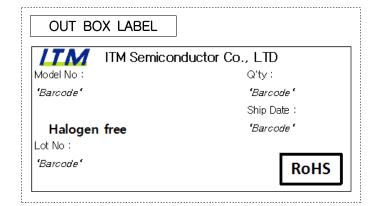

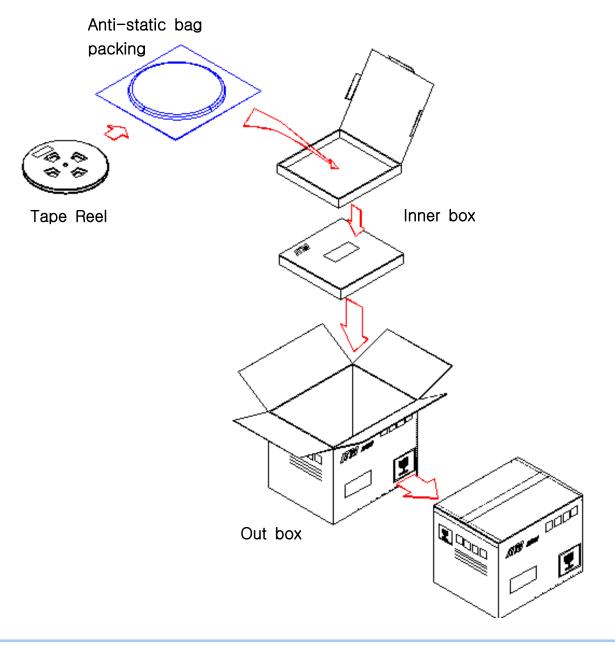

## DOUTER BOX PACKING SPECIFICATION

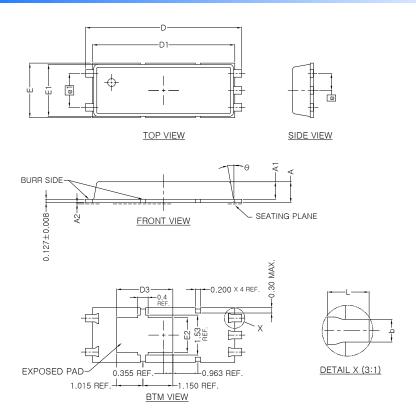

## ■ Package Description

| CVMDOI | SYMBOL DIMENSIONS |          |       |      |  |

|--------|-------------------|----------|-------|------|--|

| STMBOL | MIN.              | NOM.     | MAX.  | NOTE |  |

| A      | 0.750             | 0.800    | 0.850 |      |  |

| A1     | 0.623             | 0.673    | 0.723 |      |  |

| A2     | -                 | -        | 0.050 |      |  |

| D      | 5.900             | 6.000    | 6.100 |      |  |

| D1     | 5.320             | 5.370    | 5.420 |      |  |

| D3     |                   | 2.220 R  | ĒF.   |      |  |

| E      | 2.000             | 2.100    | 2.200 |      |  |

| E1     | 1.950             | 2.000    | 2.050 |      |  |

| E2     |                   | 1.330 R  | EF.   |      |  |

| θ      | -                 | -        | 10 °  |      |  |

| е      |                   | 0.650 BS | 3C    |      |  |

| e1     |                   |          |       |      |  |

| L      | 0.350             | -        | -     |      |  |

| b      | 0.255             | 0.300    | 0.390 |      |  |

#### NOTE

- NOTE

1. LEAD BURR: VERTICAL MAX 0.025

HORIZONTAL MAX 0.025

BURR SIDE: ALL TOP SIDE

2. MOLD BURR & FLASH: PACKAGE OUT LINE BURR MAX 0.100

EXPOSED PAD FLASH MAX 0.200

3. PACKAGE WARPAGE MAX 0.025

4. LEAD AND EXPOSED PAD PLATING: PURE TIN

THICKNESS> 7.62~25.4um

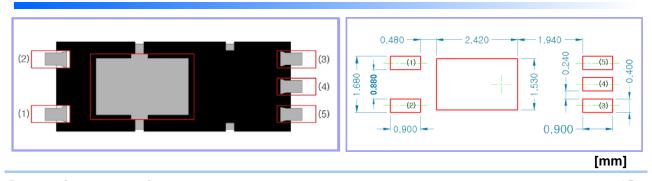

## ■ Recommend Land Pattern (time shorar)

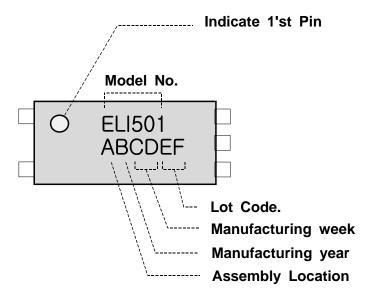

# **■** Marking Contents